Neural Processing Unit (NPU) Integration for Accelerated AI

Neural Processing Units (NPUs) are specialized hardware accelerators designed to handle the unique computational demands of AI workloads, particularly those involving deep learning. Unlike traditional CPUs or GPUs, NPUs are optimized for matrix operations, low-precision arithmetic, and parallel data processing, making them highly efficient for inference and training tasks. Their architecture enables significant improvements in performance per watt, which is especially critical in edge devices and mobile platforms.

Key Takeaways

- Specialized hardware addresses the limitations of CPUs/GPUs in handling modern AI workloads.

- On-device processing eliminates cloud dependency for faster, more secure operations.

- Parallel computing architectures enable efficient execution of neural network calculations.

- Low-power designs make advanced AI features feasible in mobile and edge devices.

- Cross-industry applications range from consumer tech to mission-critical industrial systems.

Redefining Computational Priorities

Redefining computational priorities in the context of NPU integration means rethinking how system resources are allocated to match the evolving demands of AI workloads. Modern AI tasks, such as profound neural network inference, rely heavily on tensor operations and parallelism, which general-purpose CPUs handle inefficiently. NPUs shift this balance by dedicating silicon area and memory bandwidth to AI-specific tasks, reducing latency and power consumption for everyday AI operations.

Operating systems and schedulers must know NPU resources and optimize task delegation accordingly, often requiring new APIs and driver models. At the application level, developers are encouraged to offload compatible parts of their workloads, like convolutional layers or matrix multiplications, to NPUs to unlock performance gains. This reallocation of computational priorities signals a broader trend in computing: specialization is becoming essential as AI becomes a dominant workload.

Bridging Biology and Technology

Bridging biology and technology through NPUs reflects a deeper alignment between artificial neural networks and their biological inspiration. While biological neurons process information in massively parallel and energy-efficient ways, traditional computing systems have struggled to replicate this behavior efficiently. NPUs are designed to mirror some of the structural and functional principles of the brain, such as parallel signal propagation and low-precision communication, allowing machine learning models to run in ways that more closely resemble cognitive processes.

At the system level, this convergence influences how AI models are architected and deployed. Spiking neural networks, neuromorphic chips, and adaptive learning circuits are all part of the broader trend of making machines learn and adapt like biological organisms. NPUs, while not fully neuromorphic, play a foundational role in this transition by supporting highly efficient training and inference at scale. They enable real-time sensory fusion in robotics, autonomous vehicle navigation, and context-aware decision-making in medical devices, all areas where biology has long excelled.

Understanding NPUs: Key Features

- AI-Centric Architecture. NPUs are built to efficiently handle tensor operations and high levels of parallelism, outperforming CPUs and GPUs on AI workloads by focusing only on operations relevant to neural networks.

- Low-precision Arithmetic. Most NPUs rely on reduced-precision formats like INT8 or FP16, which significantly lower power consumption and memory usage without major accuracy loss in inference.

- On-Chip Memory and Bandwidth Optimization. NPUs typically include high-speed on-chip memory and custom data paths to reduce bottlenecks in data movement, which is often a limiting factor in AI performance.

- Framework and Compiler Integration. Modern NPUs are supported by toolchains that integrate with popular AI frameworks (e.g., TensorFlow, PyTorch), enabling developers to compile and optimize models specifically for the target NPU architecture.

What Are These Specialized Processors

Specialized processors like NPUs are part of a new generation of hardware accelerators that prioritize task-specific performance over general-purpose flexibility. Their internal design is tailored to efficiently execute the dataflow patterns and memory access schemes typical of modern neural networks. These units often operate asynchronously from the main CPU, with their scheduling logic and memory hierarchies, enabling parallel processing of AI tasks without blocking other system functions. In embedded systems, this separation is crucial, as it allows real-time AI features to run continuously without overloading the host processor or draining the battery.

Their ability to deliver high inference throughput while maintaining system-level power efficiency, especially when deployed in edge AI scenarios, makes them stand out among other AI chips. For example, NPUs in consumer electronics can process visual or audio input locally, reducing the need for cloud communication and minimizing latency. Their silicon layout often includes dedicated memory banks, DMA controllers, and compression units, which help maintain high data reuse and avoid unnecessary energy expenditure. These processors also enable dynamic workload partitioning, offloading only the compute-heavy segments of a model while leaving control logic to general-purpose cores.

Architectural Innovations Driving Performance

Modern NPUs achieve their efficiency through specialization and a series of architectural breakthroughs that prioritize throughput, locality, and parallelism. One key innovation is systolic array structures, which allow data to flow rhythmically across processing elements with minimal control overhead. This structure reduces memory bandwidth pressure and highly utilizes compute units critical for deep learning inference at scale. Many NPUs also feature hierarchical memory systems with on-chip SRAM caches close to compute blocks, cutting down latency and energy waste from frequent external memory access.

Another crucial innovation is the integration of adaptive precision handling, where the NPU dynamically selects the optimal bit width for each operation based on model sensitivity and resource availability. This flexibility enhances both power efficiency and performance, especially in edge AI scenarios where workloads must be tuned to fit within tight energy budgets. Some architectures also incorporate programmable microcontrollers or custom instruction decoders, enabling finer-grained control over execution without compromising real-time response.

The Role of NPUs in Accelerated AI: Deep Learning and Beyond

While NPUs are primarily designed to speed up deep learning inference, their role in the AI ecosystem expands beyond traditional neural networks. They now support many model architectures, including transformers, graph neural networks, and reinforcement learning agents, demanding high compute density and efficient memory access. NPUs enable deploying such advanced models directly in embedded systems, allowing for localized intelligence in industrial automation, robotics, and innovative environments.

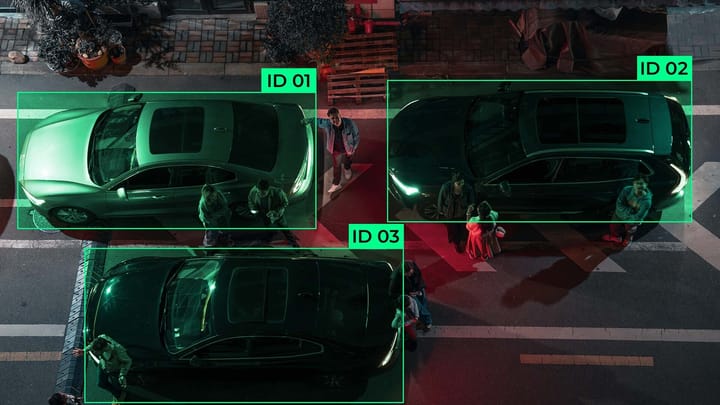

In edge AI, NPUs enable real-time performance for workloads like video analytics, speech synthesis, and anomaly detection without depending on cloud-based computation. As AI workloads diversify, NPUs are designed with programmable layers and hardware abstraction interfaces that support rapid adaptation to new algorithms. This is key for future-proofing AI chips in fast-changing environments, where models evolve quickly but hardware needs to remain stable and efficient.

Enhancing Deep Learning Workloads

NPUs significantly improve the execution of deep learning workloads by optimizing key operations such as convolutions, matrix multiplications, and activation functions that dominate neural network computations. Their architecture enables massive parallelism and data reuse, accelerating training and inference phases while maintaining strict power efficiency requirements. Complex models can run locally in embedded systems and edge AI devices with minimal latency and energy consumption, supporting real-time applications like object detection and natural language processing.

Developers can tailor computation precision to specific layers or tasks, balancing accuracy with resource use, which is crucial in scenarios with limited power budgets or thermal constraints. These processors also facilitate seamless integration with popular AI frameworks, enabling smoother model deployment and optimization pipelines.

Comparing NPUs with CPUs, GPUs, and TPUs in AI Hardware

CPU (Central Processing Unit).

- A general-purpose processor designed for a wide range of tasks.

- Excels at sequential processing and complex control logic but is inefficient for parallel AI workloads.

- Limited power efficiency for deep learning tasks due to a lack of specialized hardware.

- Commonly used for preprocessing, orchestration, and running lightweight AI models.

- Found in nearly all computing systems, including those with embedded systems.

GPU (Graphics Processing Unit).

- Designed for highly parallel tasks like graphics rendering and well-suited for matrix operations in AI.

- Provides substantial acceleration for training and inference with large neural networks.

- Higher power consumption than NPUs can limit deployment in edge AI or low-power devices.

- Flexible and programmable, supporting a wide variety of AI models and frameworks.

- Widely adopted in data centers and workstations for both training and inference.

TPU (Tensor Processing Unit).

- Google developed a custom ASIC specifically to accelerate tensor operations in neural networks.

- Optimized for large-scale training and inference, primarily in cloud environments.

- Focused on high throughput and energy efficiency, but generally not used in low-power or embedded contexts.

- Less flexible for non-tensor workloads compared to GPUs or NPUs.

- Powers Google's internal AI services and is available via cloud APIs.

NPU (Neural Processing Unit).

- Specialized AI chip designed exclusively for neural network acceleration, focusing on inference and increasing support for training.

- Highly efficient in terms of power efficiency, making it ideal for edge AI and embedded systems.

- Employs low-precision arithmetic and dataflow architectures tailored to AI workloads.

- Often integrated into mobile SoCs and specialized hardware for real-time AI tasks.

- Supports rapid deployment and optimization through dedicated toolchains and AI frameworks.

Architectural Advantages for Machine Learning

- Parallel Processing Units. NPUs contain many small processing elements working simultaneously, enabling massive parallelism for operations like matrix multiplications, which are common in machine learning.

- Dataflow Optimization. Architectures are designed to minimize data movement by optimizing data reuse and local memory access, reducing latency and energy consumption, which is critical for power efficiency.

- Low-Precision Computation Support. NPUs efficiently handle low-bitwidth formats (INT8, FP16), accelerating computation while maintaining accuracy, which suits resource-constrained edge AI devices.

- Specialized Memory Hierarchy. On-chip memory buffers and caches close to compute units reduce bottlenecks from external memory access, increasing throughput and lowering power use in embedded systems.

- Custom Instruction Sets and Hardware Accelerators. NPUs implement AI-specific instructions and fixed-function units for everyday neural network operations, streamlining execution and improving overall machine learning performance.

- Dynamic Precision and Sparsity Handling. Adaptive precision and support for sparse data reduce unnecessary computation, enhancing speed and power savings for varied ML workloads.

- Integration with AI Frameworks and Toolchains. Hardware-software co-design enables seamless model compilation and optimization, speeding development and deployment on specialized AI chips.

- Real-Time Processing Capability. Architectures support low-latency inference suitable for edge AI applications like autonomous systems, robotics, and sensor fusion, where timely decisions are crucial.

Energy Efficiency and Performance Optimizations in NPUs

NPUs are engineered to maximize energy efficiency by minimizing unnecessary data movement and exploiting hardware-level optimizations tailored to AI workloads. One key approach is leveraging on-chip memory hierarchies that reduce power-hungry access to external DRAM, a significant energy drain in traditional architectures. NPUs also implement low-precision arithmetic units that perform calculations using INT8 or FP16 formats, significantly lowering power consumption without substantially sacrificing model accuracy. These processors often incorporate dynamic voltage and frequency scaling (DVFS) to adapt power usage based on workload intensity, improving power efficiency for batch processing and real-time inference tasks.

Performance optimizations in NPUs include exploiting data sparsity by skipping zero or near-zero values during computations, which reduces the total number of operations and speeds up processing. Architecturally, NPUs use parallel processing arrays, such as systolic or spatial architectures, that enable continuous data flow and high utilization of compute units. Efficient scheduling algorithms and workload partitioning allow NPUs to balance workloads between CPUs, GPUs, and themselves within heterogeneous AI chips.

Low Precision Arithmetic and Energy Savings

Using reduced-bit formats like INT8 or FP16 instead of traditional 32-bit floating-point, NPUs perform more operations per clock cycle while consuming less energy. This reduction in data size also decreases memory bandwidth demands. It lowers the volume of data transfers, which are significant factors in energy consumption, especially in embedded systems and edge AI devices. Despite the lower bit width, carefully designed quantization techniques ensure that model accuracy remains high, making low-precision arithmetic a practical trade-off for real-world AI applications.

Furthermore, low-precision computation enables NPUs to pack more processing elements into the same silicon area, increasing parallelism and throughput without increasing power draw. This density advantage supports real-time AI workloads in compact, power-sensitive environments like mobile devices, smart cameras, and IoT nodes.

Summary

Neural Processing Units (NPUs) represent a new class of hardware focused on accelerating AI computations with minimal energy use. They leverage specialized architectures and precision-tuned operations to efficiently handle complex neural network tasks within compact, power-limited environments. By minimizing data movement and optimizing hardware resources, NPUs enable responsive, local AI processing critical for real-time applications in autonomous devices and smart sensors. Their integration into modern computing platforms supports diverse AI models and workflows while maintaining scalability.

FAQ

What is an NPU?

An NPU (Neural Processing Unit) is a specialized AI chip designed to accelerate neural network computations with high power efficiency. It is optimized for tasks like deep learning inference, especially in edge AI and embedded systems.

How do NPUs differ from CPUs and GPUs?

NPUs focus exclusively on AI workloads, using low-precision arithmetic and parallelism to deliver faster performance with less power consumption than general-purpose CPUs and GPUs. This makes them ideal for embedded systems and edge AI devices.

Why is power efficiency important for NPUs?

Power efficiency enables NPUs to perform complex AI tasks while consuming minimal energy, which is crucial for battery-operated edge AI devices and embedded systems that operate under strict power constraints.

What role do NPUs play in edge AI?

NPUs enable real-time AI processing directly on edge devices, reducing latency and avoiding the need for cloud connectivity. This supports applications like smart cameras and autonomous sensors.

How do NPUs handle data movement efficiently?

NPUs use on-chip memory and optimized dataflows to minimize energy-expensive data transfers between processors and memory. This reduces latency and improves overall power efficiency.

What is the significance of low-precision arithmetic in NPUs?

Using INT8 or FP16 formats allows NPUs to process more operations per cycle with less energy, maintaining accuracy while reducing memory and computing demands, which is critical for embedded and edge AI.

How do NPUs integrate with existing AI software frameworks?

NPUs provide toolchains and compilers compatible with popular frameworks like TensorFlow and PyTorch, facilitating seamless model deployment and optimization on AI chips.

What architectural features of NPUs improve machine learning performance?

Features like systolic arrays, hierarchical memory, and dynamic precision contribute to high throughput and low power consumption, which are vital for edge AI and embedded systems.

Why are NPUs critical for future intelligent devices?

As AI moves closer to the edge, NPUs enable autonomous, low-latency decision-making with minimal power use, supporting the growth of innovative, connected devices in energy-sensitive environments.

Comments ()